-

Characteristic Impedance Formulas Commonly Referenced:

- Microstrip: The formula Z = {87 / [sqrt(Er + 1.41)]} * ln[5.98H / (0.8W + T)] applies where W is the trace width, T is the trace copper thickness, H is the distance from the trace to the reference plane, and Er is the PCB material’s dielectric constant. This formula is valid for 0.1 < (W/H) < 2.0 and 1 < Er < 15.

- Stripline: The formula Z = [60 / sqrt(Er)] * ln{4H / [0.67π(T + 0.8W)]} is used where H is the distance between the two reference planes, with the trace centrally placed between them. This formula applies when W/H < 0.35 and T/H < 0.25.

-

Can a Ground Line be Added Between Differential Signal Lines? Generally, adding a ground line between differential signal lines is not advisable as it disrupts the beneficial coupling effects inherent to differential signaling, such as flux cancellation and noise immunity. Introducing a ground line can break this coupling effect.

-

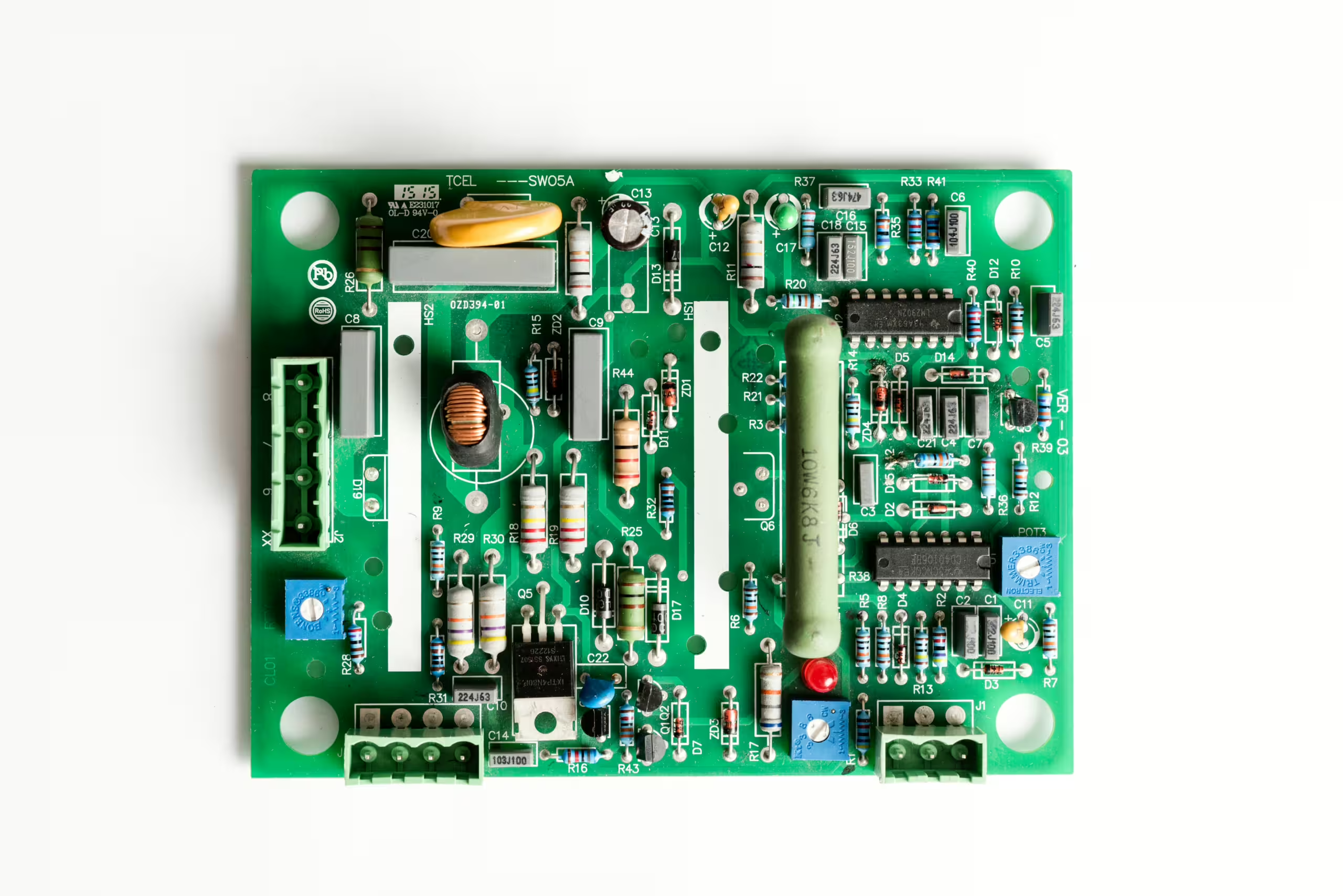

Is Specialized Design Software Required for Rigid-Flex PCB Designs? Where Can Such PCBs be Manufactured in China? Flexible Printed Circuits (FPCs) can be designed using standard PCB design software and produced in the Gerber format. Manufacturing techniques differ from those of standard PCBs, with each manufacturer setting their own limitations on minimum trace width, spacing, and via sizes. Copper reinforcement can be added at flex points for added strength. Manufacturers can typically be found by searching for “FPC” online.

-

What Are the Principles for Properly Selecting PCB to Chassis Grounding Points? The principle for selecting PCB to chassis grounding points is to use chassis ground to provide a low-impedance path for returning current and to control the path of this current. Typically, near high-frequency devices or clock generators, PCB ground layers are connected to the chassis ground using mounting screws to minimize the area of the current loop, thus reducing electromagnetic radiation.

-

What Are the Key Areas to Consider When Debugging PCBs? For digital circuits, three key aspects should be verified in sequence:

- Ensure all power supply values meet design requirements. Systems with multiple power supplies may have specific requirements regarding the sequence and speed of power-ups.

- Verify that all clock signals operate at the correct frequencies and that signal edges are free of non-monotonic issues.

- Check if the reset signals meet specified requirements. If these are in order, the chip should output its first cycle signal. Further debugging should follow based on system operational principles and bus protocols.

-

How to Manage Increased Wiring Density in PCBs with Fixed Dimensions Without Affecting Signal Integrity? In high-speed (>100MHz) and high-density PCB designs, crosstalk is a major concern. Key considerations include:

- Ensuring consistent and matched characteristic impedance along traces.

- Managing trace spacing, typically at least twice the trace width. Simulation can help determine the impact on timing and signal integrity, identifying the minimum tolerable spacing.

- Choosing appropriate termination methods.

- Avoiding parallel trace routing on adjacent layers, and especially avoiding directly overlapping traces as this can increase crosstalk.

- Using blind/buried vias to increase routing area, though this increases manufacturing costs. While exact parallelism and equal length are challenging to achieve, efforts should be made to approximate these as closely as possible.

- Reserving differential and common-mode terminations can mitigate impacts on timing and signal integrity.

-

Why Might LC Filters Sometimes Perform Worse Than RC Filters? The effectiveness of LC versus RC filters depends on the target frequency band and the appropriateness of the inductance value chosen. Inductive reactance, which varies with inductance and frequency, might not be adequate if the noise frequency is low and the inductance value is insufficient, resulting in poorer performance compared to RC filtering. However, RC filters consume power through the resistance, reducing efficiency, and the selected resistor must be capable of handling the required power.

-

How to Choose Inductor and Capacitor Values for Filtering? When selecting inductor values, consider the noise frequency you wish to filter out and the transient current response capability. If the output side of an LC filter needs to handle sudden high currents, too large an inductor value can slow down the current flow, increasing ripple noise. The capacitor value depends on the permissible ripple noise specifications; lower ripple requirements lead to larger capacitance values. The ESR/ESL of the capacitor also plays a role. For LC filters at the output of switching regulators, the influence of the poles/zeros generated by the LC on the stability of the negative feedback control loop must also be considered.

-

How to Meet EMC Requirements Without Incurring Excessive Costs? Increased costs on PCBs due to EMC compliance typically arise from adding more ground layers to enhance shielding and including components like ferrite beads or chokes to suppress high-frequency harmonics. Additionally, other mechanical shielding structures are usually required to ensure the entire system meets EMC standards. Design techniques to reduce electromagnetic emissions from circuits include:

- Using devices with slower signal slew rates to reduce high-frequency components.

- Carefully positioning high-frequency devices away from external connectors.

- Ensuring impedance matching and planned return current paths for high-speed signals to reduce reflections and emissions.

- Placing sufficient and appropriate decoupling capacitors at device power pins to mitigate noise on power and ground layers, paying attention to capacitor frequency response and temperature characteristics.

- Appropriately segmenting ground near external connectors and connecting connector grounds directly to the chassis ground.

- Potentially using ground guard/shunt traces near particularly high-speed signals, but being mindful of their impact on trace characteristic impedance.

- Retreating the power layer by 20H from the ground layer, where H is the distance between these layers.

-

Why Is It Common Practice to Separate Digital and Analog Grounds in PCBs Containing Both Digital and Analog Blocks? Separating digital and analog grounds is essential because digital circuits generate noise on power and ground during high-low state transitions, the magnitude of which depends on the signal speed and current. If the ground plane is undivided and digital circuit noise is significant, it can interfere with nearby sensitive analog circuits, even if digital and analog signals do not cross paths. Thus, separating digital and analog grounds is only unnecessary when the analog circuit area is sufficiently distant from noisy digital circuits.

-

What Is the Reasoning Behind Not Segmenting the Ground Plane While Ensuring Digital and Analog Signal Traces Do Not Cross in a PCB Layout? The requirement that digital and analog signal traces do not cross stems from the fact that the return current path of a moderately fast digital signal will closely follow the trace beneath it back to the signal source. If digital and analog signal traces were to cross, the return current noise could impact the analog circuit area.

-

How to Address Impedance Matching in High-Speed PCB Schematic Design? Impedance matching is a crucial element in high-speed PCB design, where the impedance is directly related to the routing style, such as whether the trace is on the surface layer (microstrip) or inner layers (stripline/double stripline), distance to the reference layer (power or ground), trace width, and PCB material. Impedance can only be accurately determined after routing. Simulation software may not account for discontinuities in impedance due to limitations in the models or mathematical algorithms used, so it’s typical to reserve space for terminators, like series resistors, in the schematic to mitigate the effects of these discontinuities. The ultimate solution, however, lies in careful routing to avoid impedance discontinuities.

-

Where Can One Find Accurate IBIS Model Libraries? The accuracy of IBIS models directly affects simulation outcomes. Essentially, an IBIS model represents the electrical characteristics of an actual chip’s I/O buffer, typically derived from SPICE models (which can also be measured, though with more limitations). Since SPICE data is closely linked to chip manufacturing, different chip manufacturers will have varying SPICE data for the same device, resulting in different information in the converted IBIS models. Therefore, if a device from Manufacturer A is used, only they can provide the most accurate model data for their products. If the provided IBIS models are inaccurate, the only solution is to continuously request improvements from the manufacturer.

-

What Should Designers Consider Regarding EMC/EMI Rules When Designing High-Speed PCBs? EMI/EMC design must consider both radiated (high frequency, >30MHz) and conducted (low frequency, <30MHz) emissions. A good EMI/EMC design starts with the layout, considering device placement, PCB layering, critical interconnect routing, and device selection. Failing to arrange these elements optimally in advance can complicate later fixes, increasing costs. For instance, positioning clock generators away from external connectors, routing high-speed signals in inner layers while ensuring impedance matching and continuous reference layers to reduce reflections, selecting devices with lower signal slew rates to decrease high-frequency components, choosing decoupling/bypass capacitors with appropriate frequency responses to reduce noise on power layers, and ensuring the return paths for high-frequency signal currents minimize loop area (hence reducing loop impedance) to decrease radiation. Using segmented ground layers can help control the extent of high-frequency noise. Lastly, appropriately selecting PCB to chassis grounding points is crucial.