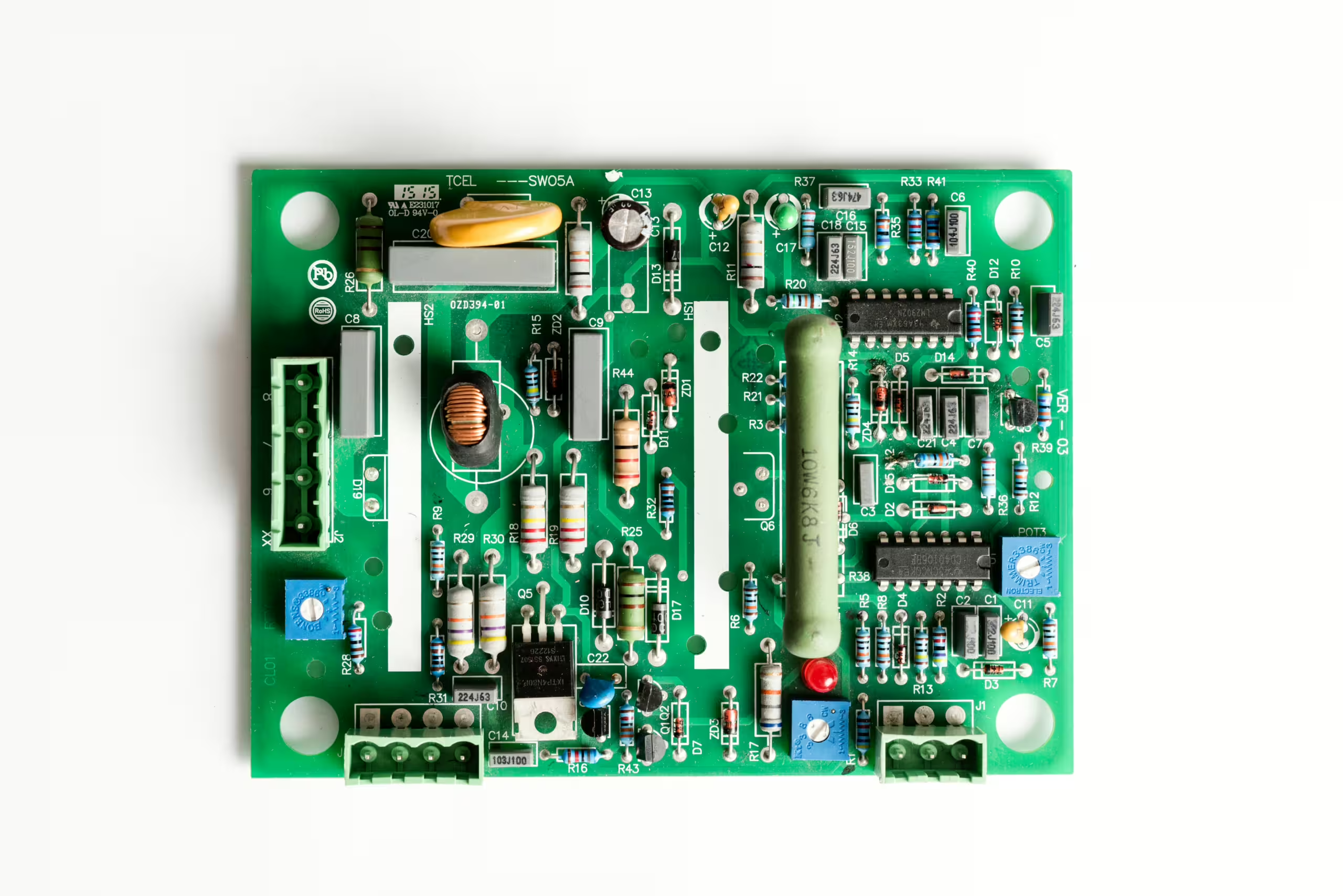

PCB Design Faces Many Challenges, including size constraints, mechanical integration, thermal considerations, and power efficiency. Additionally, Electromagnetic Compatibility (EMC) adds complexity to launching new products, presenting new obstacles in the design process.

EMC encompasses a wide range of electromagnetic phenomena, including the unintentional generation, propagation, and reception of electromagnetic energy. EMC issues can hinder the normal operation of a PCB or interfere with nearby electronic systems.

This article aims to explore the most common EMC problems encountered in the PCB design process and provide practical strategies to minimize their impact.

Layer Stacking

- Layer stacking defines the arrangement of conductive and non-conductive layers within a PCB. These layers are defined by:

- Conductive layers: number, order, materials, and copper weight

- Non-conductive layers: number, order, dielectric materials, and thickness

- PCBs can range from simple single-layer designs to complex multi-layer systems. Due to the increasing demand for high-frequency signals and small component sizes, most PCBs today have four or more layers.

- Proper arrangement of these layers can bring many benefits to the EMC and signal integrity behavior of a PCB. Thus, layer stacking is one of the most critical decisions when designing a new PCB.

- Careful planning of stacking (including proper layer order, grounding, and shielding) can minimize crosstalk and impedance mismatches. Altering the stack in the later stages of the PCB design cycle can be particularly difficult and time-consuming. Therefore, defining a robust PCB stack configuration early in the design can save a great deal of time and effort.

- Layer stacking defines the arrangement of conductive and non-conductive layers within a PCB. These layers are defined by:

Parasitic Impedance

- PCB traces themselves possess inherent resistance, inductance, and capacitance, known as parasitic impedance. Minimizing this unwanted impedance is crucial for signal integrity and EMC.

- In your PCB design, minimizing parasitic impedance can be achieved by using short and wide connections between components. Additionally, careful component layout plays a critical role.

Return Paths

- All currents must leave a source and return, forming a circuit loop. Return currents always flow along the path of least impedance. At low frequencies, this path is the one with the least resistance. At medium and high frequencies, return currents travel along the path of least inductance.

- Return paths need to be as short as possible to avoid unnecessary radiation and coupling. This can be achieved by following basic guidelines:

- Keep components as close as possible, especially those with short rise times in their signal drivers;

- Use wide ground planes to keep inductance as low as possible;

- Use layer stacking that maintains short return paths;

- Avoid gaps in the ground plane.

Ground Connections and Reference Planes

- Grounding provides a stable reference point for electrical signals. Connecting to the ground plane through long traces or poor-quality copper planes can introduce unwanted parasitic effects.

- Ensuring a short path for current return to the ground can guarantee a low-impedance return path, while also minimizing the possibility of creating ground loops that generate radiative emissions and degrade signal integrity and EMC performance.

- Reference planes are large areas of copper used to create return paths for the ground and provide a reference for high-frequency signals. They are essential for transmission lines and are an effective, economical solution for controlling radiative emissions.

- In various PCB layers, it is common to see areas filled with large copper areas. However, these copper areas have non-zero impedance, thus introducing inductance, capacitance, and resistance. To minimize the impact of this non-ideal impedance, return paths must be as short as possible. This also means that connections between different ground planes on different PCB layers must be designed to be as low impedance as possible.

Stitching Vias

- Stitching vias can be used to achieve low impedance between planes. By adding uniformly distributed vias on the reference planes, the impedance between them can be significantly reduced, thus diminishing parasitic effects. The greatest advantage of this technique is that it does not increase the cost or complexity of the PCB.

Crosstalk

- Placing long traces close to each other can negatively impact signal integrity and EMC. The fields produced by one trace can interact with adjacent traces, leading to unwanted signal coupling, known as crosstalk.

- To reduce crosstalk:

- Increase the distance between adjacent traces;

- Reduce the distance between the trace and the reference plane;

- Add ground planes between signal layers to limit the spread of fields (shielding).

- While the first method is easy to implement, it may increase the size of the circuit board. The second method could strongly affect other aspects of the PCB, such as the manufacture of high-speed traces or impedance control.

- Other techniques for handling crosstalk include avoiding parallel trace layouts, placing components away from I/O interconnects, and isolating high-noise emitters on different layers within the stack.

Electrostatic Discharge (ESD) Protection

- PCBs often need to interface with other PCBs, power units, sensors, or other external systems and may also come into contact with humans. All these interactions can generate Electrostatic Discharge (ESD) events. These discharges are extremely brief but high in energy.

- If the circuit board needs to pass immunity tests, it is a good practice, and often necessary, to add protection elements at each connector or component entering or leaving the circuit board, especially if these components might be touched by humans.

- These protection elements can be:

- Transient Voltage Suppressors (TVS), which clamp transient events to prevent permanent damage to board components;

- Metal Oxide Varistors (MOV), which divert current away from sensitive components when voltage spikes are detected;

- Thermistors, whose resistance increases (or decreases) with temperature, providing self-regulating protection. These thermistors have both Positive Temperature Coefficient (PTC) and Negative Temperature Coefficient (NTC).

Decoupling Capacitors

- Microcontrollers, communication modules, and other active components may act as active noise sources. Decoupling capacitors (also known as bypass capacitors) can mitigate the impact of this noise.

- Decoupling capacitors filter out high-frequency noise and provide a low-impedance path for high-frequency currents. To achieve good decoupling, particular attention should be paid to:

- Placing decoupling capacitors as close as possible to the integrated circuits to shorten the path of return currents;

- Minimizing the length of ground connections to reduce the amount of parasitic inductance;

- Selecting capacitors with low Equivalent Series Inductance (ESL) and low Equivalent Series Resistance (ESR).

Traces Near Board Edges

- Traces carrying fast digital signals generate strong alternating fields. If these traces are too close to unshielded board edges, these fields may leave the circuit board, generating unwanted radiative emissions.

- Assuming the circuit board has a robust reference plane, follow these guidelines to minimize unnecessary radiation:

- Move traces towards the inner area of the circuit board;

- Add a fence of vias around the entire circuit board for shielding.

Differential Impedance

- Differential pairs are a special type of transmission line where the signal and return paths are arranged in parallel. Differential pairs need to be routed with constant impedance to avoid reflections and maintain the same length to avoid signal skew.

- To control differential impedance:

- Control the stack-up by carefully selecting the height and properties of the dielectric;

- Place a solid ground plane near the differential pairs.

- As long as the reference (ground) plane is directly below the signals, the formulas used to calculate transmission line impedance are valid. Missing ground planes or gaps within them can cause impedance mismatches, leading to losses and reflections.